16

반도체 ①

# 캐리어 웨이퍼가 필요없는 빌드업/Bump-less 초박형 웨이퍼 적층 기술

**연구자.** 송준엽, 이재학 **소속.** 반도체장비연구센터 **①** 042-868-7144, 7362

## 기술 개요

• 캐리어 웨이퍼 없이 빌드업 방식으로 초박형 웨이퍼를 적층하여 3차원 패키지 수율 향상

#### 고객·시장

• 소자업체(Foundry, Fabless, Assembly)/반도체

# 기존 기술의 문제점 또는 본 기술의 필요성

- 적층패키지 제조 시 초박형 웨이퍼의 적층에서 핸들링, 수율, 생산성에 문제가 있음

- 기존 기술은 초박형 칩을 제작하기 위하여 파손을 방지하기 위해 캐리어 웨이퍼에 임시 접합하여 핸들링 및 후속 공정을 진행하므로 공정단가가 높으며, 또한 범프를 이용하여 칩 단위로 본딩하여 적층하므로 수율 및 생산성 낮음

- 모바일 AP 및 기타 반도체 패키지는 고성능화, 경박단소화되어 가고 있는 추세임

- 현재 기존 2D 방식의 인터커넥션 패키지 제조 방법은 이러한 수요자의 니즈를 구현하데 있어 scale down의 기술적 한계에 도달하였으며, 적층 패키지 기술이 대안기술로 각광받음

## 기술의 차별성

- 캐리어 웨이퍼에 임시 접합하지 않고, 빌드업 방식으로 초박형 웨이퍼 적층패키지를 제조하므로, 초박형 웨이퍼의 핸들링이 용이하고, 수율이 향상됨

- 빌드업 방식으로 웨이퍼 레벨로 적층 패키지를 제작하므로, 수율 및 양산성이 높으며, bump-less로 관통전극 및 수직인터커넥션을 동시에 구현하므로, 피치 미세화가 가능함

- 웨이퍼 레벨로 빌드업으로 적층하는 방법으로 부가적인 캐리어 웨이퍼 사용없이 쉽게 초박형 웨이퍼 핸들링 및 적층이 가능하고 칩 레벨 적층기술에 비해 높은 수율 및 양산성을 갖는 기술임

- 범프 형성없이 수직으로 인터커넥션 및 관통전극을 형성하는 방법으로, 미세 피치화 및 본딩 신뢰성 확보가 가능함

#### KIMM CORE TECHNOLOGIES 2024

유사환경 파일럿 상용모델의 자료조사 프로젝트 기술개념 프로토타입 상용데모 양산 및 기초석명 개념 또느 시작품 현장실증 개발 및 초기시진 OHOLEIGH 제작·평가 치전하 진입 개발 (#)

기술이전

17

기타

공동연구

# 기술의 우수성

기술완성도(TRL)

희망 파트너쉽

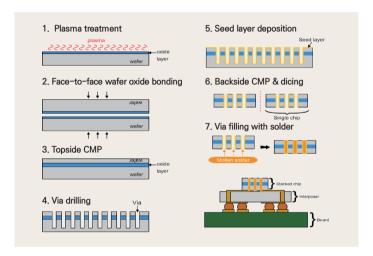

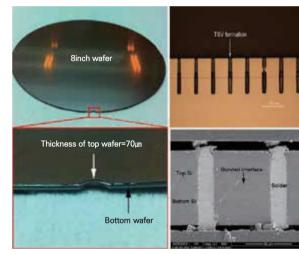

• 부가적인 캐리어 웨이퍼의 임시접합 없이 최하단의 디바이스 웨이퍼를 활용하여 초박형 웨이퍼를 쉽게 핸들링하고, 빌드업 방식으로 적층하여 관통전극 및 인터커넥션을 형성하는 기술임

라이센싱

- 최하단의 디바이스 웨이퍼를 캐리어로 활용하고, 빌드업 방식으로 웨이퍼를 본딩 및 백그라인딩하여 각 층의 웨이퍼를 박형화함

- 상기 방식으로 적층된 다층 웨이퍼에 일괄적으로 관통홀을 형성하고, 용융금속 또는 도금방식을 이용하여 bumpless 방식으로 관통전극과 동시에 각 층별 인터커넥션을 형성함

- 연구책임자 기준으로 20년 이상의 연구경력을 보유함

〈웨이퍼레벨 빌드업 Bump-less 적층 기술〉

# 지식재산권 현황

#### ≣허

- 반도체 칩 적층 패키지 및 그 제조 방법(KR1036441, PCT/KR2011/001166, SP201201174-8, US8722513)

- 반도체 칩 적층 패키지 및 그 제조 방법(KR1172533)

- 칩 접합을 위한 실리콘 기판 관통 비아, 이를 포함하는 칩, 적층 칩 및 전기도금을 이용한 적층 칩 접합방법 (KR1225253)

- 반도체 칩 적층 패키지 및 그 제조 방법(KR1036441)

#### 노하우

- Void Free Wafer Direct Bonding 기술

- Wafer 표면 전처리 기술

- Bump-less TSV(Through-Silicon Via) 형성 및 초박형 웨이퍼 빌드업 적층 기술